受託設計開発

Contracted design and development

ASIC/FPGA design

ASIC/FPGA設計

デジタル回路・アナログ回路・レイアウトの個別ブロック(セル)設計から1チップ開発までトータル的に開発いたします。

デジタル回路設計では可読性が高く、後継機種への流用を考えた汎用性の高い設計をご提案し、最適な回路を設計いたします。

1チップのレイアウトフロアプランを意識した設計により、ASIC開発の課題であるチップの縮小化を得意としており、回路規模縮小・低消費電力など、製品目的に沿ったカスタム設計をご提案いたします。

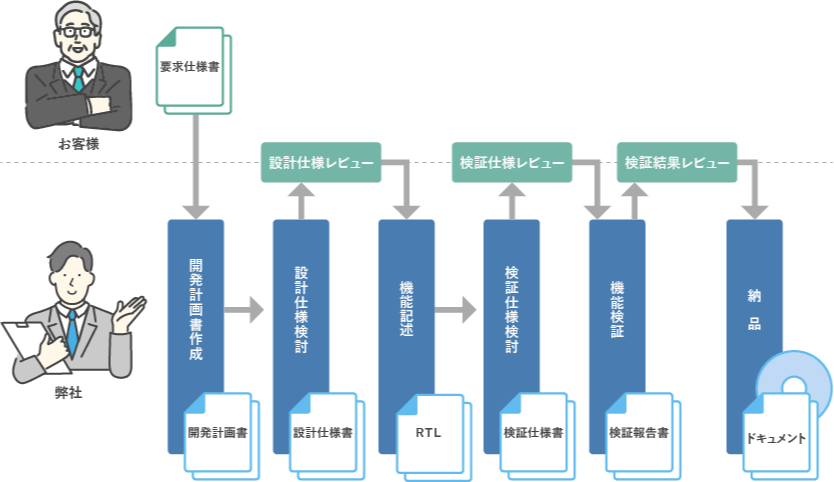

開発フロー例

開発するASIC/FPGAの要求仕様をもとに 検証・合成・レイアウト・テストまでを見通した設計仕様を作成。

設計の意図・根拠を明確にした設計で第三者でも理解できるドキュメントを提供いたします。

ASIC/FPGA設計実績

開発環境

| 使用言語 | Verilog-HDL, VHDL, SystemVerilog | |

|---|---|---|

| 開発 ツール |

論理シミュレータ | VCS, Incisive(Xcelium), ModelSim |

| 波形ビューワ | Verdi, SimVision | |

| Lint, CDC | SpyGlass, LEDA | |

| 論理合成 | Design Compiler, Synthesis | |

| バージョン管理 | Subversion, Git | |

| FPGA |

AMD: Vivado, ISE Intel: Quartus Prime Lattice Semiconductor: Lattice Diamond Microchip: Libero |

|

| FPGA使用 実績 |

AMD: Spartan, Artix, Kintex, Virtex, Zynq Intel: Cyclone, MAX Lattice Semiconductor: Mach Microchip: IGLOO, SmartFusion |

|

設計・検証品質

レイトロンでは、各段階における問題点を早期に発見し、設計の手戻りを削減する取り組みを行っております。

主な取り組みとしては、以下のことを行っております。

-

1.設計品質

- RTL設計記述作法(ガイドライン、デザインルール)に沿った設計

- Lintチェックツールでのコーディング確認

- CDCチェックツールでの確認

-

2.検証品質

- カバレッジ検証

- SystemVerilogアサーション検証

- 検証モデル作成

- 協調検証・エミュレータ検証

- プロトタイピングFPGA検証

お客様との品質・情報共有化に努めております。

サインオフに必要なチェックシート等についても柔軟に対応いたします。

開発実績

| カテゴリー | 開発事例 | 内容 |

|---|---|---|

| 映像 | バックライト制御用 | 画像処理(バックライト輝度算出, フィルタ), LEDドライバ制御, HDMI, SPI, DDR3, AXI |

| パネル特性補正 | 画像補正(パネル特性パラメータフィッティング), パネルドライバ 制御, SPI, DDR3 |

|

| 画像検品装置 | 画像処理(エッジ検出, 汚れ検出), FPGA間画像転送, PCIe, DDR4, SelectIO, Zynq |

|

| 赤外線カメラ | 撮像制御, 画像記録/再生, 可逆圧縮/伸長(内製IP), SDRAM, eMMC | |

| TV向け | 画像処理, 画像補正 | |

| カメラDSP |

ズーム, ガンマ補正, 歪み補正, ノイズリダクション, フリッカ補正, AF処理, 各種フィルタ |

|

| 制御 | 半導体装置向け | モータコントローラ制御, AD/DA制御, 光入力/基板間転送, PCIe, Aurora, DDR3 |

| 産業機器向け計測機器 | 高速AD計測, JESD204B, DDR3, MicroBlaze | |

| 複合機向け | PCIe, DDR2/3/4コントローラ, DMAコントローラ, CPUプラットフォーム | |

| 通信 | 移動体通信基地局装置 | フロントホール処理, PHY-Low処理, O-RAN |

| 移動体通信基地局負荷試験機 | フロントホール処理, O-RAN |